# A 80 MS/S CMOS SAMPLE-AND-HOLD CURRENT MODE CIRCUIT USING DOUBLE SAMPLING

تصميم دائرة من نوع CMOS لاخذ عينات من الموجات بسرعة (8 ميجا عينة في الثانية بنظام التيار وباستخدام معدل تعبين مزدوج

> Hamed Elsimary, Electronics Research Institute, Cairo, Egypt

> > خلاصه :

يقدم هذا البعث تصميما لدائرة الكثرونية متكاملة باستخدام تكنولوجيا - CNIDS وتعمل هذه الدائرة التي نقوم بأدد عينات من الموجسسات التناظرية المراد تحويلها الى رقمية بنظام التيار وتتسم هذه الدائرة مانها نقوم بالخذ عدد مضاعف من العينات في غس الرمن وذلك بحقى ضعف المعدل الدول ولان بحسمت على عنول المتهاك القدرة وتتسم هذه الدائرة مانها المضا بكونها كاماة التيابي أي أدا ذات مخرجين كل منهما عكس الأخر حتى بدكر تناشى و الزالة الشوشرة الناتجة عن عملية أخذ عينات الدوحات وقد تم نمتيل وعرض بدائج الدائرة من خلال هذا الدحث

Abstract. A fully differential CMOS sample and hold circuit (S/D) in current male using double sampling technique is presented. Double sampling technique, gives a factor of two increase in the sampling rate while maintaining comparable power consumption and circuit complexity in comparison with the conventional Soft configuration. A precise current mirror circuit with low injut impedance is adopted. A fully differential configuration for placing the switches were used to cancel the sample switches feed-through error. Also, the clock controlling the sample switches is boosted so as to make their on resistance low. The circuit is designed and simulated in 0.5 µm CMOS technology using BSIM3v3 device parameters. Simulation results show a 10-bit operation at the sampling rate of 80 M1 sample/sec with 10mW power dissipation at 3V supply.

Keywords: Sample and hold eircuits, current mode, double sampling

### 1. Introduction

In most Analog to Digital converters A/Ds, the front end sample and hold block is very important. The speed and accuracy of the converter is highly dependent on the performance of the S/H circuit

The fastest S/H circuits operate in open loop gain mode [1], [2]. However, their accuracy tends to be limited. Closed loop configuration make at possible to achieve higher resolution, but the required high gain limits the speed of the circuit.

Fig. 1 shows a basic open loop sample and hold circuit. The gain of this S/H circuit is one which is suitable for front end circuits. The operation of the circuit consists of two phases: the sample phase and the hold phase. In the sample phase the input signal is sampled in the capacitor  $C_h$  through the switch  $S_1$ . In the hold phase the switch is open and the sample is held on the capacitor, and buffered through the buffer B1. According to this discussion the buffer, or the op amp, if closed loop gain is used, is not optimally utilized since it is idle during the campling period. Double sampling effectively gives a factor of

## E. 43 Hamed Elsimary

two increase in the sampling rate compared to the basic S/H topology while maintaining better utilization of the circuit components which in turn leads to an improved power consumption.

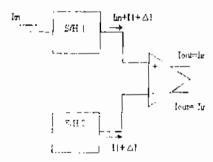

Fig. 2 represents a double-sampled S/H circuit, while the sample is taken in the upper capacitor during the period  $\phi$ , the lower one is connected in the hold configuration during the period  $\overline{\phi}$ , and the vise versa. Thus a new sample can be read from the output twice every clock cycle. The sampling rate is doubled but the double sampling scheme introduces more switches which introduces some unwanted source of errors. Source of errors in the switches and overcoming it will be discussed later.

Fig. 1. A basic open loop sample and hold circuit

Fig. 2. A double sampling S/H circuit

Because the sample and hold circuit presented in this work operates in the current mode, a precise high performance current initror is needed as an important part of the circuit and will be discussed in the following section

#### 2. High performance current mirror circuit

The current mirror is dominant part of the current mode approach, in this work we adopted a circuit presented in [3]. Fig. 3. Shows a conventional MOS current mirror circuit, In this circuit the drain or gate voltage of M1 changes when the ioput signal current I<sub>m</sub> changes. Voltage change at the input node can be expressed as:

$$\Delta I = \frac{\Delta I_m}{g_{-}} \tag{1}$$

where gin is the transconductance of M1. This causes the drain to source voltage of M1 to differ from that of M2 as a result a current mismatch between I<sub>m</sub> and I<sub>cut</sub> is introduced.

Fig. 1. Conventional MOS current mirror

Similarly when V at changes, Implehanges due to the finite output resistance of M2, it can be expressed as:

$$\Delta I_{\text{opt}} = \frac{\Delta V_{\text{opt}}}{r_{\text{opt}}} \tag{2}$$

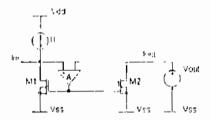

. ig. 4. High accuracy current mirror

Fig. 4. Shows a circuit that can minimize the dependence of the voltage change on the current change at, the input the voltage change is suppressed by the gain of the op-amp and becomes as follows:

$$\Delta I' = \frac{M_m}{A \cdot g_m} \tag{3}$$

# E. 45 Hamed Elsimary

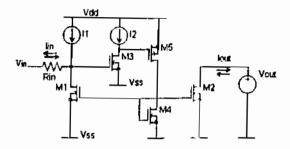

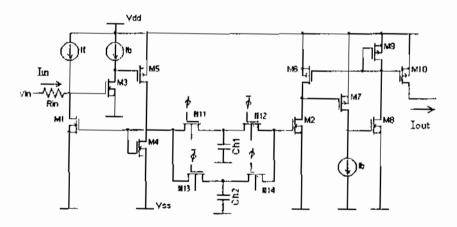

Fig. 5. Realization of the accurate current mirror

Fig. 5 shows the actual realization of the suggested current mirror presented conceptually in fig. 4 Transistors M3 through M5 and the bias current source I2 form the amplifier. Same technique can be done at the output side to enhance the output resistance of the current mirror in order to reduce the change in the output current lout due to the change in the output voltage V<sub>out.</sub> This way an improved current mirror can be achieved. In the following section a description of the design of the S/H circuit will be presented.

## 3. Double sampling S/H circuit Design

Fig (6) Current mode double sampling S/H circuit

Fig. 6. Represents the design of a double sampling current mode S/H circuit by placing analog switches N11 through M14, derived by the clock phases  $\phi$  and  $\overline{\phi}$ , and the holding capacitors  $C_{h1}$ ,  $C_{h2}$ . At the clock period  $\phi$  transistor S1 turns on allowing the capacitor  $C_{h1}$  to sample signal and allowing  $C_{h2}$  to be in hold mode. At the clock period  $\overline{\phi}$ ,  $C_{h1}$  becomes in hold mode and  $C_{h2}$  in sample mode. As a result the drain source current of M10 or  $I_{out}$  is the sampled  $I_{in}$  plus the constant current 11. Transistor M5 through M10 are the PMOS based version of the circuit in fig. 5 required for enhancing the output impedance of the current mirror for accurate current ratio. The analog switches adds unwanted source of errors, in order to reduce the switches feed through errors. The complete sample and hold circuit is implemented in a fully differential configuration as shown in Fig. 7, where two symmetrical circuits similar to the circuit of  $f_{10}$  of it connected to the a put of a differential amplifier. The first circuit passes current equal to  $\frac{1}{12}\Delta I$ , where  $\frac{1}{12}\Delta I$  is the error current due to the switches first shough. The output of the differential amplifier cancels the circuit current due to the switches first shough. The output of the differential amplifier cancels the circuit.

Fig 7. Differential Sample and Hold Configuration

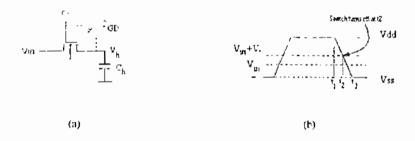

Fig. 8. Switch feed through effect in MOS switch (a) Switch, (b) Gate voltage waveform

## E. 47 Hamed Elsimary

Also the figure shows that the error due to switches feed through cancel each other, however, means for redu fing switches feed through errors needs to be addressed.

#### 4. Sources for sampling error

One of the most serious factors affecting the performance of the high precision CMOS sample-and-hold circuits is charge injection due to clock feed through [4]. Fig. 8 shows the effect of the charge injection an NMOS switch, when the clock signal goes from Vdd to Vss the switch turns off at  $t_2$ . From  $t_3$  to  $t_3$  the switch is off and charge is injected into the S/H capacitor  $C_h$  from  $C_{GD}$  (the parasitic capacitor between the rate and the drain of the switch). As a result, the voltage across the capacitor is decreased. This introduces a pedestal error  $\delta V_h$  which can be expressed as:

$$\delta V_{H} = \frac{C_{GD}}{C_{H} + C_{GD}} (V_{in} + V_{i} - V_{is})$$

(4)

where  $V_t$  is the transistor's threshold voltage,  $C_h$  is the hold capacitor,  $C_{GD}$  is the parasitic capacitor between the gate and drain.

It can be seen from (4) that the feed-through results in an offset which is a serious problem in high precision sample and hold circuits. Several methods have been proposed to overcome this problem. These includes charge cancellation by adding during MOS transistors, offset voltage cancellation by adding a network [4], and by using miller hold capacitance [5], and by minimizing the dependence of the feed through error on the input signal [6]. However, charge cancellation methods are sensitive to device parameters. It is worth mentioning that reducing the size of the switch transistor leads to a small  $C_{\rm gd}$  which result in reduction of the feed through error as seen in equation (2). In this paper, the differential eonfiguration is used to cancel the switch feed through.

Other source of error is the on resistance of the MOS switch. In CMOS technology the switch can be implemented with a single NMOS or a single PMOS transistor. The NMOS switch offers low on-resistance when operated near the negative supply voltage but the closer the input signal to the positive supply voltage the less conductive the switch becomes eventually it is cut off one threshold voltage below the supply. The operation of the PMOS is just the opposite A CMOS switch or transmission gate may be used, it offers a finite on resistance in the whole voltage range between the supplies. Another possibility to achieve the same is to control the single transistor switch with a gate voltage greater in magnitude than the supply voltage, thus a voltage boosting circuit is required.

### 5. Simulation Results

The designed circuit is—simulated using Spiee in 0.5 um CMOS using BSIM3v3.1 Device parameters. Fig. 8 shows the functional simulation of the double sampling current mode S/H circuit. The switches used are NMOS transistor with of W=10um L=1um, and aspect ratio=W/L=10,  $C_{h1}=C_{h2}=0.3$ pf. The input current was varied from -200uA to +200uA, the supply voltage is 3V, while the gate voltage is boosted to

5V. The output is plotted as shown in Fig. 9. The current error is calculated at different sample steps and plotted as shown in fig. 9, the figure displays the maximum of .48uA of error current for the various sample steps included in the rising edge of the input, and 0.45 uA in the falling edge. The effect of the clock feed through is almost completely eliminated. The error signal becomes the half bit equivalent error for 10-bit accuracy. The circuit is found to dissipate 10mw, the folded cascode configuration makes the circuit suitable for low voltage applications.

Class. Function I simulation of the S/H circuit

Fig 10 Current Error at different sample steps

## E. 49 Hamed Elsimary

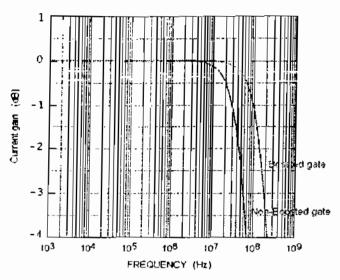

Fig. 11. Frequency response of the S/H

Fig 11 simulates the frequency response of the sample and hold circuit where the input current signal was 200uA peak to peak, the figure shows a 3db frequency bandwidth of 200 MHz for the circuit with boosted gate voltage, while that for the circuit with non boosted gate voltage is 60MHz

#### 6. Conclusion

Simulation results represent that a double sample S/H circuit with 40 MHz clock, has a double sampling rate of 80 Ms/s. Results also shows error current suitable for 10-bit accuracy.

#### References

- [1] P. Vorenkamp and J. P. M. Verdaasdonk, "Fully Bipolar, 120-Msamples/s 10-b Track-and-hold Circuit," (EEE J. Solid-State Circuits, no. 27, pp. 998-992, 1992.

- [2] M. Waltari, and K. Halonen, "A 220-Msamples/s CMOS. Sample-and-Hold Circuit Using Double Sampling," Analog Integrated Circuits and Signal Processing Journal, vol. 18, pp. 21-31, 1999.

- [3] Y. Sugimoto, and S. Imai, "The Design of a 1V, 40 MHz, Current Mode Sample-and Hold Circuit with 10-BIT Linearity," ISSCC '99, pp II-132-II-135, 1999.

- [4] D. Johns, and K. Martin, "Analog Integrated Circuit design," John Wiley Pub., 1997.

- [5] P.J. Lim and B. Wooley, "A High-Speed Sample-and-Hold technique using a Miller hold capacitance," IEEE J Solid State Circuits, vol (26) no.(4) pp. 643-651, 1991.

- [6] M.F. Li, S.Y. Yep, and Y. C. Lim, "A Novei Integrated CMOS Switch for High Precision Sample-and-Hold Technique," Analog Integrated Circuits and Signal Processing, vol. 12, pp. 211-215, 1997.